# M\_CAN Modular CAN IP-module

# Functionalities and Features

White Paper M\_CAN\_WP001

Document Revision 2.0 01.07.2015

Robert Bosch GmbH Automotive Electronics

### LEGAL NOTICE

© Copyright 2015 by Robert Bosch GmbH and its licensors. All rights reserved.

"Bosch" is a registered trademark of Robert Bosch GmbH.

The content of this document is subject to continuous developments and improvements. All particulars and its use contained in this document are given by BOSCH in good faith.

NO WARRANTIES: TO THE MAXIMUM EXTENT PERMITTED BY LAW, NEITHER THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS AND CONTRIBUTORS, NOR ANY PERSON, EITHER EXPRESSLY OR IMPLICITLY, WARRANTS ANY ASPECT OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, INCLUDING ANY OUTPUT OR RESULTS OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO UNLESS AGREED TO IN WRITING. THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO IS BEING PROVIDED "AS IS", WITHOUT ANY WARRANTY OF ANY TYPE OR NATURE, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND ANY WARRANTY THAT THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO IS FREE FROM DEFECTS.

ASSUMPTION OF RISK: THE RISK OF ANY AND ALL LOSS, DAMAGE, OR UNSATISFACTORY PERFORMANCE OF THIS SPECIFICATION (RESPECTIVELY THE PRODUCTS MAKING USE OF IT IN PART OR AS A WHOLE), SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO RESTS WITH YOU AS THE USER. TO THE MAXIMUM EXTENT PERMITTED BY LAW, NEITHER THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS CONTRIBUTORS, NOR ANY PERSON EITHER EXPRESSLY AND OR IMPLICITLY, MAKES ANY REPRESENTATION OR WARRANTY REGARDING THE APPROPRIATENESS OF THE USE, OUTPUT, OR RESULTS OF THE USE OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO IN TERMS OF ITS CORRECTNESS, ACCURACY, RELIABILITY, BEING CURRENT OR OTHERWISE, NOR DO THEY HAVE ANY OBLIGATION TO CORRECT ERRORS, MAKE CHANGES, SUPPORT THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, DISTRIBUTE UPDATES, OR PROVIDE NOTIFICATION OF ANY ERROR OR DEFECT, KNOWN OR UNKNOWN. IF YOU RELY UPON THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, YOU DO SO AT YOUR OWN RISK, AND YOU ASSUME THE RESPONSIBILITY FOR THE RESULTS. SHOULD THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL LOSSES, INCLUDING, BUT NOT LIMITED TO, ANY NECESSARY SERVICING, REPAIR OR CORRECTION OF ANY PROPERTY INVOLVED TO THE MAXIMUM EXTEND PERMITTED BY LAW.

DISCLAIMER: IN NO EVENT, UNLESS REQUIRED BY LAW OR AGREED TO IN WRITING, SHALL THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS OR ANY PERSON BE LIABLE FOR ANY LOSS, EXPENSE OR DAMAGE, OF ANY TYPE OR NATURE ARISING OUT OF THE USE OF, OR INABILITY TO USE THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, INCLUDING, BUT NOT LIMITED TO, CLAIMS, SUITS OR CAUSES OF ACTION INVOLVING ALLEGED INFRINGEMENT OF COPYRIGHTS, PATENTS, TRADEMARKS, TRADE SECRETS, OR UNFAIR COMPETITION.

INDEMNIFICATION: TO THE MAXIMUM EXTEND PERMITTED BY LAW YOU AGREE TO INDEMNIFY AND HOLD HARMLESS THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS AND CONTRIBUTORS, AND EMPLOYEES, AND ANY PERSON FROM AND AGAINST ALL CLAIMS, LIABILITIES, LOSSES, CAUSES OF ACTION, DAMAGES, JUDGMENTS, AND EXPENSES, INCLUDING THE REASONABLE COST OF ATTORNEYS' FEES AND COURT COSTS, FOR INJURIES OR DAMAGES TO THE PERSON OR PROPERTY OF THIRD PARTIES, INCLUDING, WITHOUT LIMITATIONS, CONSEQUENTIAL, DIRECT AND INDIRECT DAMAGES AND ANY ECONOMIC LOSSES, THAT ARISE OUT OF OR IN CONNECTION WITH YOUR USE, MODIFICATION, OR DISTRIBUTION OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, ITS OUTPUT, OR ANY ACCOMPANYING DOCUMENTATION.

GOVERNING LAW: THE RELATIONSHIP BETWEEN YOU AND ROBERT BOSCH GMBH SHALL BE GOVERNED SOLELY BY THE LAWS OF THE FEDERAL REPUBLIC OF GERMANY. THE STIPULATIONS OF INTERNATIONAL CONVENTIONS REGARDING THE INTERNATIONAL SALE OF GOODS SHALL NOT BE APPLICABLE. THE EXCLUSIVE LEGAL VENUE SHALL BE DUESSELDORF, GERMANY.

MANDATORY LAW SHALL BE UNAFFECTED BY THE FOREGOING PARAGRAPHS.

INTELLECTUAL PROPERTY OWNERS/COPYRIGHT OWNERS/CONTRIBUTORS: ROBERT BOSCH GMBH, ROBERT BOSCH PLATZ 1, 70839 GERLINGEN, GERMANY AND ITS LICENSORS.

### **Revision History**

| Version | Date       | Remark                                        |

|---------|------------|-----------------------------------------------|

| 1.0     | 26.11.2010 | First version for M_CAN 2.0                   |

| 2.0     | 01.07.2015 | New revision for M_CAN Revision 3.0.0 - 3.2.1 |

### Conventions

The following conventions are used within this document:

Register Names **RXBC**

#### References

This document refers to the following documents:

| Ref | Author    | Title                          |

|-----|-----------|--------------------------------|

| [1] | AE/PJ-SCI | M_CAN User's Manual            |

| [2] | AE/PJ-SCI | M_CAN System Integration Guide |

### Terms and Abbreviations

This document uses the following terms and abbreviations:

| Term                                          | Meaning                                                                                                                                          |

|-----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| CAN<br>M_CAN<br>Rx<br>Tx<br>IF<br>RAM<br>FIFO | Controller Area Network<br>Modular Controller Area Network<br>Receiver<br>Transmitter<br>Interface<br>Random Access Memory<br>First In First Out |

| CPU                                           | Central Processing Unit                                                                                                                          |

| ECC                                           | Error Correction Code                                                                                                                            |

| VHDL                                          | VHSIC Hardware Description Language                                                                                                              |

### **Table of Contents**

| 1   | Introduction                             | 1 |

|-----|------------------------------------------|---|

| 2   | M_CAN Integration                        |   |

| 3   | Message RAM                              |   |

| 3.1 | Introduction                             |   |

| 3.2 | Partitioning                             | 2 |

| 3.3 | Facts                                    | 3 |

| 4   | Operation of the M_CAN                   | 4 |

| 4.1 | Basic Configuration                      |   |

| 4.2 | Message Transmission                     | 4 |

| 4.3 | Message Reception                        | 4 |

| 5   | Tx Handler                               |   |

| 6   | Rx Handler                               | 7 |

| 7   | Message Filtering (Range, Dual, Classic) | 8 |

| 8   | Safety                                   |   |

| 9   | Miscellaneous                            |   |

# 1 Introduction

The M\_CAN white paper was created to help the first time users to understand the M\_CAN functionalities and features. This document is applicable to M\_CAN versions 3.0.0, 3.0.1, 3.2.0 and 3.2.1.

## 2 M\_CAN Integration

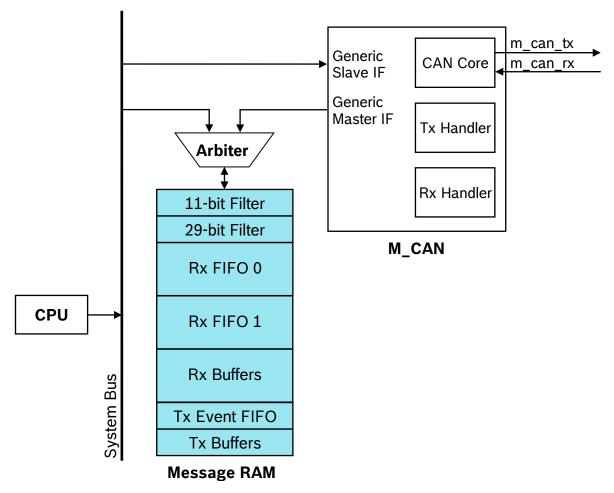

Figure 1 shows how the  $M_{CAN}$  IP module can be integrated into a system. The  $M_{CAN}$  consists of three main parts.

- The **CAN Core** implements the functionality required to perform communication in a CAN bus system. Therefore it generates the M\_CAN\_Tx signal and processes the M\_CAN\_Rx signal.

- The **Tx Handler** in the M\_CAN performs all the tasks related to message transmission.

- The **Rx Handler** in the M\_CAN performs all the tasks related to message reception.

Figure 1: Integration of M\_CAN IP module into a system

## 3 Message RAM

### 3.1 Introduction

The Message RAM serves as memory for the M\_CAN. The following types of data can be stored in the Message RAM:

- Message ID Filter Elements

- Receive Messages (in RX FIFO0, in RX FIFO1, in RX Buffers)

- Transmit Messages (in TX Buffers)

- TX Event Element

The Message RAM needs to be accessible for the CPU and the M\_CAN. If the Message RAM implementation has just a single interface, an Arbiter is required to grant access to the Message RAM. Figure 1 shows how the Message RAM can be connected to the M\_CAN.

### 3.2 Partitioning

To operate the M\_CAN the Message RAM has to be partitioned into memory sections. Partitioning is an agreement between CPU and M\_CAN regarding, where in the Message RAM to store which type of elements, e.g. the M\_CAN knows from where to fetch the messages to be transmitted. The Message RAM in Figure 1 contains the recommended partitioning: e.g. the first memory section should hold the 11-bit Filter elements, the second section the 29-bit Filter elements, etc.

In general the following rules should be met.

- The individual sections should be back to back. Sections are not allowed to overlap.

- The order of the sections can be arbitrary.

- Each section should be large enough to fit all according elements: e.g. if an RX FIFO1 should be able to hold 20 maximum size CAN FD frames, then dimension the section accordingly.

Bosch delivers the M\_CAN with an excel sheet that allows to calculate the required Message RAM size.

- The Message RAM size required for an M\_CAN that uses all features is bounded to a maximum value.

- A section in the Message RAM may also be 0 in size if the feature is not used: e.g. if RX FIFO1 is not used, then the corresponding memory section can be 0

The CPU configures the following information into the M\_CAN

- Start addresses of the memory sections in the Message RAM The Start address is given relative to the Message RAM.

- Number of elements in each section E.g. the number of elements in the RX FIFO1.

• The size of the elements in some sections All sections that hold CAN messages can be adjusted in size, e.g. if the largest transmitted CAN FD frame will have just 32 bytes payload, this is configured. This allows saving Message RAM memory.

The default configuration of the M\_CAN is that all sections contain 0 elements in the Message RAM.

#### 3.3 Facts

- a) Multiple M\_CAN controllers may share the same Message RAM. Each M\_CAN controller has its own Message RAM section assigned. Sharing Tx and Rx message buffers of different M\_CAN controllers is not recommended. Automated gateway functions are not supported.

- b) The Message RAM content is not affected by a reset of the M\_CAN. The behavior of the Message RAM depends on the system implementation.

- c) The Message RAM, including the parity and ECC logic, is not part of the M\_CAN deliverables.

- d) Arbitration logic, necessary for connecting several M\_CANs to one Message RAM instance, is not part of the M\_CAN deliverables.

# 4 Operation of the M\_CAN

### **4.1** Basic Configuration

The CPU configures the M\_CAN by reading/writing the registers in the M\_CAN. The basic things to be configured are:

- Bit timings

- Enabling interrupts and selecting the interrupt lines

### 4.2 Message Transmission

The general steps for transmission of a message are described in this section.

#### Configuration

For the M\_CAN to behave as a transmitting node, the CPU configures the fundamental Tx registers like **TXBC**, **TXESC** etc.

#### Message Transmission

- 1) The messages that should be transmitted are first written into the Message RAM in the section allocated for the Tx Buffers.

- 2) In order to request the transmission of a message, the CPU has to write to the appropriate bits in the **TXBAR** register of the M\_CAN.

- 3) When a request to transmit a message is received by the M\_CAN, the Tx handler scans the Message RAM (Tx Buffers) for the highest priority message and transmits this message.

### 4.3 Message Reception

The general steps for reception of a message are described in this section.

#### Configuration

- 1) For the M\_CAN to behave as a receiving node, the fundamental Rx registers like **RXBC**, **RXFnC**, **and RXESC** etc. have to be configured by the CPU. These registers define among others where the messages are stored.

- 2) Acceptance filtering of the received messages can be done by configuring registers **GFC**, **SIDFC** and **XIDFC**.

#### Message Reception

- 3) If acceptance filtering is configured, the CPU has to write the standard/extended message ID filters into the Message RAM.

- 4) When a message is received by the M\_CAN, the Rx handler does the acceptance filtering according to the GFC, SIDFC and XIDFC configurations. The Rx handler compares the ID of the received message with the ID's in the filter elements. If it finds a match, it stores/discards the received message according to the filter element configuration.

- 5) After filtering, if the message is to be stored, it will be stored either in an Rx FIFO or a Dedicated Rx buffer in the Message RAM, according to the filter element configuration.

- 6) The M\_CAN can inform the CPU via interrupts (if configured) that a new message has arrived.

- 7) The CPU reads the Rx Buffer/FIFO status registers of the M\_CAN to find out where the M\_CAN had stored the message in the Message RAM.

- 8) The CPU reads the message from the Message RAM.

- 9) The CPU acknowledges the message by writing to an M\_CAN register.

### 5 Tx Handler

- a) The M\_CAN supports 32 Tx buffers. The Tx buffers can be configured as dedicated Tx buffers, Tx FIFO, or Tx queue and as combination of dedicated/FIFO or dedicated/queue Tx buffers.

- b) There exists no separate "message valid" flag. A message which is requested for transmission is send out as soon as the CAN bus is available.

- c) Pending transmissions are signalled in an own register ("Tx Buffer Request Pending").

- d) The Tx handler scans all Tx buffers with activated transmission request, in case of the Tx FIFO the oldest pending Tx FIFO buffer. The scan result is assorted according to the priority of the message ID. The Tx message with the highest priority message ID is send out first.

- e) A requested message can be cancelled (transmit cancellation flag).

- f) The information about each occurred transmission, including a Tx time stamp, can be found in the Tx event FIFO. There exist two transmit events: "Tx event" (successful transmission) and "Transmission in spite of cancellation" (transmission after late Host cancellation)

- g) A successfully cancelled transmission is signalized in an own register ("Tx Buffer Cancellation Finished").

- h) Remote frame handling is not implemented. The reception of a remote frame will not trigger the transmission of a message.

### 6 Rx Handler

- a) Successfully received and filtered messages are stored in one of the two receive FIFOs or in a dedicated Rx buffer. Each receive FIFO can hold up to 64 messages. Up to 64 dedicated Rx buffers can be configured.

- b) If the receive FIFO is full, the newly arriving messages are treated according to the configured mode. Two modes are available.

- Blocking Mode: No further messages are written to the Rx FIFO until at least one message has been read out from the Rx FIFO.

- Overwrite Mode: The new message accepted in the Rx FIFO will overwrite the oldest message in the Rx FIFO.

Note: When an Rx FIFO is operated in overwrite mode and an Rx FIFO full condition is signalled, reading of the Rx FIFO elements should start at least at get index + 1. The reason for that is, that it might happen, that a received message is written to the Message RAM (put index) while the CPU is reading from the Message RAM (get index).

c) The FIFO fill level is signalized. A FIFO watermark can be configured. Dedicated interrupts can be configured. The FIFO can be cleared with one write access by resetting PUT and GET index to zero ("FIFO flush").

## 7 Message Filtering (Range, Dual, Classic)

- a) Up to 128 filter elements for 11-bit identifiers may be configured.

- b) Up to 64 filter elements for 29-bit identifiers may be configured.

- c) With the high priority message filter option, received messages can trigger a high priority message interrupt. For direct access to these messages, the respective FIFO buffer index can be read from the High Priority Message Status register.

- d) Each filter can be configured as acceptance or rejection filter.

### 8 Safety

- a) The Message RAM may be secured against bit errors. If an external circuit detects and signals a Message RAM error via (m\_can\_aeim\_beu = '1') to the M\_CAN, then the M\_CAN sets **CCCR.INIT** to '1' and enters INIT state.

- b) The READY input of the generic master interface (m\_can\_aeim\_ready) is monitored by the RAM watchdog during an access via the generic master interface (m\_can\_aeim\_select active). In case there is no response at the READY input until the watchdog counter has counted down to zero, the counter stops and interrupt flag IR.WDI is set. The counter is configurable and can be disabled. The counter is clocked by the Host clock (m\_can\_hclk).

- c) Suspend CAN operation: The Host can set the CCCR.INIT bit. While CCCR.INIT is set, message transfer from and to the CAN bus is stopped, the status of the CAN bus output can\_tx is recessive (HIGH). The counters of the Error Management Logic EML are unchanged. Setting CCCR.INIT does not change any configuration register.

### 9 Miscellaneous

- a) The M\_CAN can be set into power down mode controlled by input signal m\_can\_clkstop\_req or via CC Control Register CCCR.CSR. As long as the clock stop request signal m\_can\_clkstop\_req is active, bit CCCR.CSR is read as one. When all pending transmission requests have completed, the M\_CAN waits until bus idle state is detected. Then the M\_CAN sets the CCCR.INIT to one to prevent any further CAN transfers. Now the M\_CAN acknowledges that it is ready for power down by setting output signal m\_can\_clkstop\_ack to one and CCCR.CSA to one. In this state, before the clocks are switched off, further register accesses can be made. A write access to CCCR.INIT will have no effect.

- b) The M\_CAN is not able to detect the baud rate autonomously by monitoring the CAN bus.

- c) By hard reset, all M\_CAN registers are reset to their default values. A soft reset achieving the same result is not supported.

- d) The following bits/bit fields are set/reset with every read access to the register.

- ECR.CEL

- PSR.PXE

- PSR.RFDF

- PSR.RBRS

- PSR.RESI

- PSR.DLEC

- PSR.LEC

The destructive read accesses can be prevented with the signal **m\_can\_dis\_mord** (disable modification on read).