White Paper Revision: 1.0.0 15.03.2019

#

## Robert Bosch GmbH

Automotive Electronics (AE)

#### LEGAL NOTICE

© Copyright 2019 by Robert Bosch GmbH and its licensors. All rights reserved.

"Bosch" is a registered trademark of Robert Bosch GmbH.

The content of this document is subject to continuous developments and improvements. All particulars and its use contained in this document are given by BOSCH in good faith.

NO WARRANTIES: TO THE MAXIMUM EXTENT PERMITTED BY LAW, NEITHER THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS AND CONTRIBUTORS, NOR ANY PERSON, EITHER EXPRESSLY OR IMPLICITLY, WARRANTS ANY ASPECT OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, INCLUDING ANY OUTPUT OR RESULTS OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO UNLESS AGREED TO IN WRITING. THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO IS BEING PROVIDED "AS IS", WITHOUT ANY WARRANTY OF ANY TYPE OR NATURE, EITHER EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE, AND ANY WARRANTY THAT THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO IS FREE FROM DEFECTS.

ASSUMPTION OF RISK: THE RISK OF ANY AND ALL LOSS, DAMAGE, OR UNSATISFACTORY PERFORMANCE OF THIS SPECIFICATION (RESPECTIVELY THE PRODUCTS MAKING USE OF IT IN PART OR AS A WHOLE), SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO RESTS WITH YOU AS THE USER. TO THE MAXIMUM EXTENT PERMITTED BY LAW, NEITHER THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS AND CONTRIBUTORS, NOR ANY PERSON EITHER EXPRESSLY OR IMPLICITLY, MAKES REPRESENTATION OR WARRANTY REGARDING ANY THE APPROPRIATENESS OF THE USE, OUTPUT, OR RESULTS OF THE USE OF THIS SPECIFICATION. SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO IN TERMS OF ITS CORRECTNESS, ACCURACY, RELIABILITY, BEING CURRENT OR OTHERWISE. NOR DO THEY HAVE ANY OBLIGATION TO CORRECT ERRORS, MAKE CHANGES, SUPPORT THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, DISTRIBUTE UPDATES, OR PROVIDE NOTIFICATION OF ANY ERROR OR DEFECT, KNOWN OR UNKNOWN. IF YOU RELY UPON THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, YOU DO SO AT YOUR OWN RISK, AND YOU ASSUME THE RESPONSIBILITY FOR THE RESULTS. SHOULD THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO PROVE DEFECTIVE, YOU ASSUME THE COST OF ALL LOSSES, INCLUDING, BUT NOT LIMITED TO, ANY NECESSARY SERVICING, REPAIR OR CORRECTION OF ANY PROPERTY INVOLVED TO THE MAXIMUM EXTEND PERMITTED BY LAW.

White Paper

#### M\_CAN add-ons

DISCLAIMER: IN NO EVENT, UNLESS REQUIRED BY LAW OR AGREED TO IN WRITING, SHALL THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS OR ANY PERSON BE LIABLE FOR ANY LOSS, EXPENSE OR DAMAGE, OF ANY TYPE OR NATURE ARISING OUT OF THE USE OF, OR INABILITY TO USE THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM RELATED THERETO, INCLUDING, BUT NOT LIMITED TO, CLAIMS, SUITS OR CAUSES OF ACTION INVOLVING ALLEGED INFRINGEMENT OF COPYRIGHTS, PATENTS, TRADEMARKS, TRADE SECRETS, OR UNFAIR COMPETITION.

INDEMNIFICATION: TO THE MAXIMUM EXTEND PERMITTED BY LAW YOU AGREE TO INDEMNIFY AND HOLD HARMLESS THE INTELLECTUAL PROPERTY OWNERS, COPYRIGHT HOLDERS AND CONTRIBUTORS, AND EMPLOYEES, AND ANY PERSON FROM AND AGAINST ALL CLAIMS, LIABILITIES, LOSSES, CAUSES OF ACTION, DAMAGES, JUDGMENTS, AND EXPENSES, INCLUDING THE REASONABLE COST OF ATTORNEYS' FEES AND COURT COSTS, FOR INJURIES OR DAMAGES TO THE PERSON OR PROPERTY OF THIRD PARTIES. INCLUDING, WITHOUT LIMITATIONS, CONSEQUENTIAL, DIRECT AND INDIRECT DAMAGES AND ANY ECONOMIC LOSSES, THAT ARISE OUT OF OR IN CONNECTION WITH YOUR USE, MODIFICATION, OR DISTRIBUTION OF THIS SPECIFICATION, SOFTWARE RELATED THERETO, CODE AND/OR PROGRAM OUTPUT, RELATED THERETO, ITS OR ANY ACCOMPANYING DOCUMENTATION.

GOVERNING LAW: THE RELATIONSHIP BETWEEN YOU AND ROBERT BOSCH GMBH SHALL BE GOVERNED SOLELY BY THE LAWS OF THE FEDERAL REPUBLIC OF GERMANY. THE STIPULATIONS OF INTERNATIONAL CONVENTIONS REGARDING THE INTERNATIONAL SALE OF GOODS SHALL NOT BE APPLICABLE. THE EXCLUSIVE LEGAL VENUE SHALL BE DUESSELDORF, GERMANY.

MANDATORY LAW SHALL BE UNAFFECTED BY THE FOREGOING PARAGRAPHS.

INTELLECTUAL PROPERTY OWNERS/COPYRIGHT OWNERS/CONTRIBUTORS: ROBERT BOSCH GMBH, ROBERT BOSCH PLATZ 1, 70839 GERLINGEN, GERMANY AND ITS LICENSORS.

#### **REVISION HISTORY**

| Revision | Date       | Notes           |

|----------|------------|-----------------|

| 1.0.0    | 15.03.2019 | Initial release |

|          |            |                 |

#### References

[1] Time-stamping of CAN frames, CAN Newsletter 2/2017: https://cannewsletter.org/uploads/media/raw/3ebef2c5e26451ab4aa386e0e67ce5f2.pdf

#### **Terms and Abbreviations**

This document uses the following terms and abbreviations:

| Term  | Meaning                                                  |

|-------|----------------------------------------------------------|

| CAN   | Controller Area Network                                  |

| CRAM  | Central RAM; common memory of DMA and CPU Core           |

| DMA   | Direct Memory Access                                     |

| DMU   | DMA Interface Unit; Add-on of M_CAN of BOSCH             |

| EoF   | End of Frame; distinct position at end of CAN frames     |

| GTM   | Generic Timer Module                                     |

| M_CAN | CAN Communication Controller; IP module of BOSCH         |

| MRAM  | Message RAM; local memory of M_CAN                       |

| NoC   | Network on Chip                                          |

| NVM   | Non-Volatile Memory; e.g. Flash Memory                   |

| SoC   | System on Chip                                           |

| SoF   | Start of Frame; distinct position at start of CAN frames |

| SoF   | Start of Frame; distinct position at start of CAN frames |

| TCM   | Tightly Coupled Memory                                   |

| TSU   | Time Stamping Unit; add-on for M_CAN of BOSCH            |

|       | —                                                        |

#### **Table of Contents**

| 1     | Overview                              | . 1 |

|-------|---------------------------------------|-----|

| 1.1   | DMU add-on                            |     |

| 1.1.1 | Motivation to use a DMU               | .1  |

| 1.1.2 | TX element                            | .4  |

| 1.1.3 | RX0 / RX1 elements                    | .4  |

| 1.1.4 | TX event element                      | . 5 |

| 1.1.5 | DMU register                          | . 5 |

| 1.1.6 | DMU Debug section                     | . 5 |

| 1.1.7 | Data flow within the SoC              | . 5 |

| 1.2   | TSU add-on                            | . 6 |

| 1.2.1 | Receipt of messages with timestamp    | . 6 |

| 1.2.2 | Sending messages with timestamp       | . 6 |

| 1.2.3 | Synchronization process after AUTOSAR | . 6 |

| 1.2.4 | Saving time stamps at SoF             | . 6 |

### **1** Overview

To support modern CAN networks, Bosch has extended the functionality of M\_CAN in form of two hardware add-ons. The DMU add-on allows reduction of CPU load by offloading the transport of CAN messages to a DMA controller. The TSU expansion module enables hardware based and AUTOSAR compatible time synchronization with the best possible precision.

#### 1.1 DMU add-on

#### **1.1.1** Motivation to use a DMU

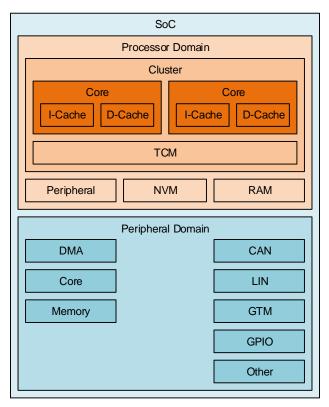

When exchanging CAN messages between the CPU Core and the M\_CAN, there are some issues to consider, especially for complex SoCs. Due to the high complexity of modern SoC architectures, the OnChip communication paths are divided into several domains of different performance. The bridging between domains additionally slows down performance, e.g. due to clock-domain crossings.

Figure 1: Domains of a SoC

The heat-map (red = fast, blue = slow) in Figure 1 illustrates the speed of data transfers initiated by CPU Core in the Processor Domain. Thus, the connection of the CPU cores to the dedicated caches is the fastest, followed by the TCM within the cluster. When creating the SW, it must be ensured that these memories can be used efficiently. In extreme contrast to this are the accesses to components in the peripheral domain. For single access, performance can be 30 times slower.

If, for example, the continuous exchange of CAN messages between the CPU core and an M CAN is considered, the following interactions are typically required:

- Check the status register of M CAN when asserting an interrupt

- Optionally transfer the CAN messages •

- Optionally signal to the M CAN the completion message transfers

If the CPU cores in the Processor Domain would perform these interactions, they would be significantly slowed down by the NoC. For example, such interactions can also be done via a CPU core within the Peripheral Domain, if available. However, this article focuses on a different approach that does not allocate computational resources of any CPU core.

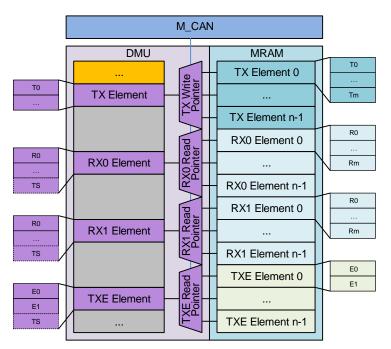

Bosch offers an add-on for the M CAN called DMU. With this, the continuous exchange of CAN messages can be completely outsourced to a DMA controller. The add-on is based on the concept of virtualizing the FIFO head elements, s. Figure 2.

Figure 2: Functional block diagram of DMU

The M CAN has an associated message RAM (MRAM), which i.a. contains the elements (CAN messages) organized in FIFOs, shown on the right. To access the memory segment of the current message (head element) within these FIFOs by the CPU, the respective pointers (Read / Write Pointer) from the M CAN must previously be gueried. To avoid this, accesses to fixed address areas are virtualized. The DMU dynamically redirects these accesses to the head elements in the MRAM. The redirection is controlled invisibly within the DMU by the FIFO pointers in the M CAN. The size of the reserved areas correspond to the largest possible message elements, which are 18 words for the TX, RX0 and RX1 elements and 2 words for the TX Event element (3 words if the TSU Timestamp is also transferred). The transfer of a last element word activates a process in the DMU, in which for TX elements the transmit request is set in M CAN, or for the other elements (RX0, RX1, TXE) the dedicated

White Paper

M\_CAN add-ons

FIFO-Acknowledge is set in M\_CAN. Thus, writing / reading the CAN messages via DMU elements completes the whole enqueueing / dequeueing process in the M\_CAN. The DMU supports messages transfers from the CRAM to the TX FIFO / Queue and vice versa, from the RX FIFOs / TX Event FIFO to the CRAM.

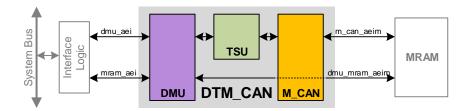

The following block diagram (Figure 3) shows the M\_CAN with the add-ons DMU and TSU. The CPU accesses to the M\_CAN are routed through both add-on modules.

Figure 3: M\_CAN subsystem with DMU and TSU

Figure 4 shows the memory map of the DMU. In the yellow marked memory area starting at address 0, the registers of the M\_CAN and the TSU are memory mapped. Afterwards, the purple coloured Virtual Buffers are shown, which are accessed by the DMA in order to transport the head elements of the M\_CAN message FIFOs.

White Paper

#### DMU\_AEI - 0x000 S Register (512 byte) - 0x200 **TX Element** 0x280 **RX0** Element DMU 0x300 **RX1** Element 0x380 TX Event Element 0x3C0 Registers 0x400 TX Element 0x480 RX0 Element DMU Debug 0x500 RX1 Element - 0x580 TX Event Element MRAM AEI 0x000 RAM **MRAM** sade (n byte)

Figure 4: DMU address map

#### **1.1.2 TX element**

Here the CAN message elements are written by the DMA controller to be added in the TX FIFO / Queue. When writing the last element word, the TX request is automatically set for this element, so that the M\_CAN sends this. The DMU requests further CAN message elements from the DMA controller as long as the TX FIFO / Queue is not full.

#### 1.1.3 RX0 / RX1 elements

Here the CAN message elements are read by the DMA controller which are located in the receive FIFOs 1 or 2 of the M\_CAN. When the last element word is read, the dequeuing is communicated to the M\_CAN by setting the dedicated acknowledge index by the DMU. Optionally, the time stamp of the TSU can also be transmitted. The DMU triggers the DMA to dequeue further CAN message elements as long as the RX FIFO is not empty.

#### **1.1.4 TX event element**

Like the RX0 / RX1 elements, but here the TX events are read, optionally with the time stamp of the TSU.

#### **1.1.5 DMU register**

The DMU gets most of the configuration parameters from the M\_CAN, only the transport of the HW timestamp of the TSU can be switched on / off here. Various status information provides feedback on whether the access to the virtual elements were correct or, if not, what problem occurred. This is particularly helpful when debugging the DMA routines, but should also be monitored during normal operation for reasons of Functional Safety.

#### **1.1.6 DMU Debug section**

When debugging the software, the DMU elements can be accessed by reading, without affecting the enqueuing of dequeuing of the DMA. For the TX element, the last element written is read, for the RX0, RX1, TXE elements the current element is read. These accesses do not trigger automatisms of the DMU, like the acknowledgment in M\_CAN.

#### **1.1.7** Data flow within the SoC

The following approach is recommended for the data flow within the SoC: A RAM has to be selected to which the desired CPU core can access with the highest possible read / write performance and to which the DMA controller also has direct access. This CRAM is then used to exchange the CAN messages, with the DMA controller taking over the slow transfers of the CAN messages across large distances of the NoC and storing the messages in the CRAM close to the CPU core, which then access without performance loss.

#### 1.2 TSU add-on

For the AUTOSAR (Automotive Open System Architecture) compatible synchronization of time bases between CAN nodes, only software implementations had been used due to a lack of special hardware. To further increase the time accuracy, special hardware is required. Document CiA 603 specifies a hardware-based concept, which is now available as an M\_CAN add-on called TSU. This approach is independent of interrupt response times and thus achieves the best possible accuracy. The TSU may operate on its own internal timebase, or uses an external time base, e.g. a reference time base within the SoC.

#### **1.2.1** Receipt of messages with timestamp

To configure the M\_CAN to receive a time-stamped message, a base / extended message ID filter element must be configured accordingly, i.e. SO.SSYNC = 1 or F1.ESYNC = 1. Upon receipt of a valid message matching the filter, the time stamp is stored in the TSU. Since the TSU stores several time stamps, a pointer is written into the CAN message (R1.RXTSP), which points to the corresponding entry in the TSU. When reading out such an RX messages with the DMU, the TSU time stamp can be automatically attached.

#### **1.2.2** Sending messages with timestamp

If a time stamp has to be generated when a CAN message is sent, the following bits must be set in the message: T1.TSCE = 1 and T1.EFC = 1. Upon successful transmission, a time stamp is stored in the TSU and a TX Event message is generated, which refers to the corresponding entry in the TSU, i.e. field TXTSP in event message word E1 (E1.TXTSP). When using DMU, the time stamp of the TSU can also be automatically attached.

#### **1.2.3** Synchronization process after AUTOSAR

After successful configuration (see above) of all participating CAN nodes, the timers of the time slaves can be corrected with a two-step synchronization process. In the first step, the current time T0 is latched in the time master, and the part of T0, which represents the seconds, is sent to the time slaves with the SYNC message. If the EoF is reached when sending this SYNC message, then timestamps are stored in the TSUs of all nodes, i.e. in the Time Master and all Time Slaves. This is the common point of time reference. In the second step, the time master adds its TSU time stamp to the nanosecond part of T0 and sends it to the time slaves via FollowUp message. From this, the time slaves can derive their own time base. A detailed description of the time synchronization is described here [1].

#### **1.2.4** Saving time stamps at SoF

For non-AUTOSAR applications, the TSU can also be configured to store timestamps at the start of a CAN message (SoF bit).